Understanding Virtual Memory with Paging

Virtual Memory: Expanding the Horizons of Computer Memory

In the world of modern computing, the concept of virtual memory is fundamental to the efficient utilization of limited physical memory resources. Virtual memory, in conjunction with a Memory Management Unit (MMU) and a mechanism called paging, allows systems to handle memory in a way that appears virtually limitless. This article delves into the key components and workings of virtual memory with paging.

What is Virtual Memory?

Virtual memory is a memory management technique that provides the illusion of having more physical memory than is actually available. It does this by creating an address space larger than the physical memory capacity of a system. This expanded address space is divided into fixed-size blocks called “pages.”

The Memory Management Unit (MMU)

At the heart of virtual memory lies the Memory Management Unit (MMU). The MMU is a hardware component responsible for translating virtual addresses to physical addresses. It plays a pivotal role in managing the interaction between the CPU, applications, and the physical memory.

When a program or process runs, it generates virtual addresses, which are mapped to physical memory addresses by the MMU. This translation process is where paging comes into play.

Paging and the Page Table Base Register (PTBR)

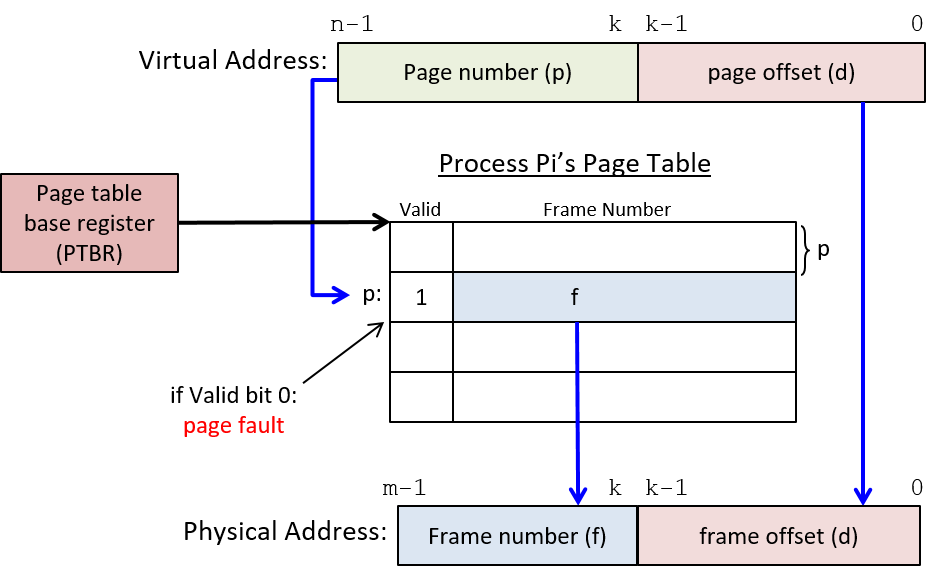

Paging is a memory management scheme used to manage virtual memory efficiently. In a paged system, the virtual address space is divided into fixed-size pages, and the physical memory is divided into equally sized page frames. The Page Table Base Register (PTBR) is a crucial component of the paging system.

Each process running on a computer has its own unique page table. The PTBR is a hardware register within the MMU that stores the base address of the page table for the currently executing process. This means that each process has its own page table, allowing for isolated memory management.

Storing PTBR in the Process Control Block (PCB)

To ensure that the MMU knows which PTBR to use for a given process, the operating system maintains a data structure known as the Process Control Block (PCB). The PCB contains information about the state of each process, including the PTBR value.

The Context Switch: Swapping PTBR via PCB

During a context switch, when the operating system switches from one process to another, it involves a series of crucial steps. One of these steps is the exchange of the PTBR through the PCB. Here’s how the context switch unfolds:

-

The operating system manages the context switch, saving the state of the current process and loading the state of the new process.

-

The PTBR value for the new process, which is stored in the new process’s PCB, is loaded into the MMU.

-

As the new process begins execution, the MMU utilizes the PTBR to translate virtual addresses to physical addresses, ensuring that the process operates within its own isolated memory space.

Handling Invalid Virtual Pages

In a paged virtual memory system, the concept of an “invalid virtual page” is crucial. When a process attempts to access a virtual page that is currently not stored in RAM, a situation known as a “page fault” occurs. This page fault indicates that the accessed virtual page does not have a valid mapping to a physical frame in RAM.

Here’s what happens when a virtual page is found to be invalid:

-

Page Fault Occurs: When the Memory Management Unit (MMU) encounters a Page Table Entry (PTE) with a valid bit set to zero, it triggers a page fault exception. The valid bit being zero indicates that there is no valid mapping for the virtual page in question.

-

OS Intervention: In response to the page fault, the operating system intervenes. It takes the following steps to resolve the issue:

-

Finding a Free Frame: The OS identifies a free frame (e.g., frame j) of RAM into which it will load the faulted page.

-

Reading from Disk: It issues a read operation to load the page from disk into the identified frame j of RAM.

-

Updating the Page Table Entry: After the read from disk is completed, the OS updates the Page Table Entry (PTE) for the faulted page. It sets the frame number to j and the valid bit to 1, signifying a valid mapping. This PTE now holds a valid mapping to frame j.

-

-

Process Resumption: With a valid mapping in the page table, the OS restarts the process at the instruction that caused the page fault. The process can now access the virtual memory address, which maps to an offset in physical frame j.

It’s important to note that in cases where there are no available free RAM frames, the OS may select a frame to replace with the faulted page. In this scenario, the page table entry of the replaced page is updated with a valid bit of 0, indicating that its mapping is no longer valid. If the replaced page was modified (dirty bit set), it is written back to disk before replacement to preserve any changes made by the process.

Understanding how the operating system handles invalid virtual pages and page faults is essential in comprehending the robust memory management provided by paging in virtual memory systems.

Keep in mind the page number and page offset is the virtual address the process wants to access.

Two level paging

The additional advantage of two-level paging is efficient utilization of physical memory and space savings compared to a single-level paging system. This is achieved due to the hierarchical structure of the page table system. Here’s how it works:

In a traditional single-level paging system, each individual page table contains all the entries for the entire virtual address space. This means that even in a system with a large virtual address space, each process requires a complete, comprehensive page table. This can lead to significant memory consumption because each page table requires a substantial number of entries to handle the entire address space, even if many parts of this address space are not used.

In contrast, two-level paging takes a different approach. There are two levels of page tables:

The outer page table: This table is on the first level and contains entries for the entire virtual address space of a process. Each entry in the outer page table points to a second level of page tables, called page table pages.

Page table pages: These are the page tables on the second level. Each page table page is responsible for a specific range of the virtual address space.

The advantage of this hierarchical approach is that the outer page table on the first level is relatively small since it contains entries for the entire virtual address space. However, each page table page on the second level is responsible for a smaller part of the address space. This means that only the parts of the address space that are actually used are described in detail in the page tables on the second level.

As not every part of a process’s virtual address space is used simultaneously, two-level paging allows for the efficient use of physical memory. Only the page table pages that are actually needed are loaded, rather than loading the entire page table. This leads to significant savings in physical memory allocation and reduces memory consumption because unused parts of the address space do not need to be detailed in the page tables. In conclusion, virtual memory with paging and the use of the Page Table Base Register (PTBR) is a key mechanism in modern computing. It allows systems to manage memory efficiently, create the illusion of abundant memory, and ensure the secure and isolated execution of multiple processes. Understanding these concepts is fundamental for anyone interested in the inner workings of memory management in computer systems.

Also two level paging helps to address another problem especially for small memory devices: The statement “Hard to find a contiguous allocation of large size” refers to the challenge of locating a single, continuous memory space that is sufficiently large to accommodate the entire page table or parts of it.

In a paging-based memory system, page tables need to be stored in physical memory for efficient access by the Memory Management Unit (MMU). However, these page tables can be quite extensive in size, especially when the system’s address space is large. This means that a large contiguous memory space is required to store the entire page table or portions of it in a single, continuous structure. With two level paging you have smaller pages.